Department of Electrical Engineering and Computer Science

#### MASSACHUSETTS INSTITUTE OF TECHNOLOGY

## 6.035 Spring 2013

# Test II

You have 50 minutes to finish this quiz.

Write your name and athena username on this cover sheet.

Some questions may be harder than others. Read them all through first and attack them in the order that allows you to make the most progress. If you find a question ambiguous, be sure to write down any assumptions you make. Be neat. If we can't understand your answer, we can't give you credit!

This exam is open book and open laptop. Additionally, you may access the course website, but aside from that you may NOT USE THE NETWORK.

Please do not write in the boxes below.

| I (xx/16) | II (xx/20) | III $(xx/27)$ | IV (xx/37) | Total $(xx/100)$ |

|-----------|------------|---------------|------------|------------------|

|           |            |               |            |                  |

|           |            |               |            |                  |

|           |            |               |            |                  |

Name:

Athena username:

### I Generating Assembly for References

In this question, you'll generate code to implement C++'s pass-by-reference features in Decaf. In C++, if a function declaration contains a parameter with a declaration int &x, then x is passed by *reference* meaning that 1) the function receives the address of x and 2) an assignment to x, such as x = 1, automatically dereferences the address for x and stores 1 in that location.

1. [16 points]: Generate x64 assembly code for swap.

```

void foo()

{

int a[2];

a[0] = 0;

a[1] = 1;

swap(a[0], a[1]);

}

void swap(int &r1, int &r2)

{

int t = r1;

r1 = r2;

r2 = t;

}

```

Write your assembly in AT&T syntax (src then dest). You should only use the instructions described in the table below. Remember that the first argument is passed in register rdi and the second in rsi. Finally, remember the simple x86\_64 addressing modes: %rax references register rax, (%rax) references memory at the address in rax, and 100(%rax) references memory at 100 bytes + the address in rax. Only one dereference (e.g. (%rax)) is allowed per instruction.

x86\_64 instructions to use

| enter \$n, \$0 | Adjust stack for $n$ bytes of local storage |  |  |

|----------------|---------------------------------------------|--|--|

| mov a, b       | Move value of a into destination b          |  |  |

| add a, b       | Add value of a to value in b; store in b    |  |  |

| call sym       | Call function sym                           |  |  |

| leave          | Undo effects of enter                       |  |  |

| ret            | Return from function call                   |  |  |

```

foo: swap:

enter $16, $0

mov $0, -8(%rbp)

mov $1, -16(%rbp)

mov $-8 %rdi

add %rbp %rdi

mov $-16 %rsi

add %rbp %rsi

call swap

leave

ret

```

#### II What Makes a Lattice?

**2.** [2 points]: Given a partial order  $\leq$  over a set P, for an element  $a \in P$  to be an upper bound of a set  $Q \subseteq P$ , what must be true of a?

**3.** [3 points]: Given a partial order  $\leq$  over a set P, for an element  $a \in P$  to be a least upper bound of a set  $Q \subseteq P$ , what must be true of a?

**4.** [3 points]: True/False. All infinite lattices are incomplete. If true, give a proof. If false, give a counterexample – i.e., provide an infinite lattice that is complete.

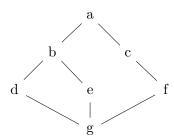

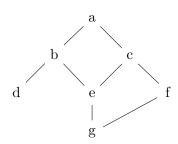

**5.** [12 points]: Each of the following Hasse diagrams describe a different partial order  $\leq_i$  for the set  $P = \{a, b, c, d, e, f, g\}$ . For each diagram, describe why  $(P, \leq_i)$  is or is not a lattice.

Α.

В.

# III Liveness Analysis

In this problem, you will perform liveness analysis on the following piece of code using a bit-vector formalization where the order of the variables in the vector is xyz:

```

x = a + b

y = x + 1

z = x

if (x > 0) {

z = x + 1

} else {

x = 2

}

y = z + x

```

**6.** [5 points]: Draw the control flow graph for this program. Label each basic block with a number n.

| 7. | [8 | points]: | Compute $\operatorname{GEN}[n]$ and $\operatorname{KILL}[n]$ for each basic block $n.$ |  |

|----|----|----------|----------------------------------------------------------------------------------------|--|

|    |    |          |                                                                                        |  |

8. [8 points]: Compute the least solution of the data flow equations, e.g. IN[n] = ... and OUT[n] = ... for each basic block. Assume that all variables are live after the end of the last basic block.

9. [6 points]: Do the results of liveness analysis on this code enable any optimization opportunities? If so, describe the optimization. If not, describe an optimization that uses liveness analysis and explain why it's not applicable.

### IV Home on The Range

Ben Bittdiddle heard that instructions like movb (move a single byte) can be faster than instructions like movq (move an entire quadword). Because of this, he'd like to build an analysis that computes the range of values that an unsigned 64-bit integer variable may have so that his compiler knows when it's safe to use these other instructions on that variable. As so often happens on tests at MIT, for some reason, you have to help him with this.

Ben knows that to analyze the range of a variable in the program, he needs to define a lattice that defines the data-flow facts that the analysis will track for the variable.

Ben chooses to define the base elements of his lattice to be from the set  $P = \{ [l, u] \mid l \leq u \text{ and } 0 \leq l \text{ and } u \leq 2^{64} \}$ . This is the set of all ranges [l, u] of bounded 64-bit unsigned integers, where l is the lower end of the range (inclusive) and u is the upper end (inclusive).

Ben then chooses the following partial order for two ranges  $[l_1, u_1] \in P$  and  $[l_2, u_2] \in P$ :

$$[l_1, u_1] \leq [l_2, u_2]$$

if and only if  $l_2 \leq l_1$  and  $u_1 \leq u_2$ .

10. [2 points]: Describe the relationship between  $[l_1, u_1]$  and  $[l_2, u_2]$  when  $[l_1, u_1] \leq [l_2, u_2]$ . Define their relationship in terms of their overlap/intersection, containment, or order.

11. [8 points]: Define the join operator,  $[l_1, u_1] \vee [l_2, u_2]$ , that is consistent with Ben's partial order.

12. [10 points]: Under Ben's partial order, is P a lattice? Why or why not? If not, explain how you would extend P to be a lattice.

13. [7 points]: When Ben's compiler runs the analysis on a program, it will maintain a single lattice element for each of the program's variables. Assume that at the program point before a statement a = b + c, the lattice element for b is  $[l_b, u_b]$  and the lattice element for c is  $[l_c, u_c]$ . What value will the transfer function compute for the lattice element  $[l_a, u_a]$  for a at the program point after the statement? Assume that  $u_b$  and  $u_c$  are less than  $2^{15}$ .

14. [5 points]: Assuming that all the transfer functions in Ben's analysis are monotonic, does his analysis terminate? Why or why not?

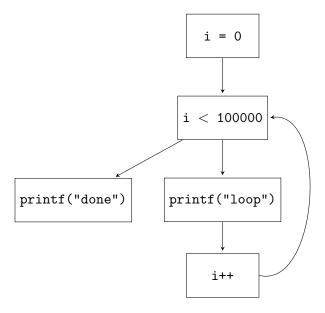

15. [5 points]: Ben implemented the data-flow framework you helped him with but is running into problems. In certain cases, it seems to take an inordinately long time, even for small code segments. So, he printed the control flow graph for one of the offending segments:

Why is this code slowing down the analysis framework? How can you fix this problem?